SPERRY RAND

# UNIVAC

IIO6 SYSTEM

SYSTEM

ERRATA SHEET TO SYSTEM DESCRIPTION. UP-7685 Programming Information Exchange Bulletin 1, UP-7700.1

- Page 6, Figure 2-1 -- Minimum system requirement is 2 UNISERVO\* VI C or 2 UNISERVO\* VIII C Magnetic Tape Units.

- Page 30, paragraph 4.7.9. -- At end of paragraph, add: "\*The j and a fields together serve to specify any of the 128 control registers."

- ■Page 51, Table of UNISERVO\* VIII C CHARACTERISTICS For TAPE SPEED, change "42.5" to read "120".

- ■Page 93, Appendix B -- For topmost word format, change "MULTIPLE" to read "MULTIPLY".

- ■Page 105, Appendix D -- In introductory sentence, change "STAT-PACK" to read "MATH-PACK".

Please mark your copies of UP-7685 according to this Errata Sheet. Bulk distribution being made is the same as distribution for UP-7685. For details refer to original bulk distribution sheet. For additional copies, this sheet and original manual order via a Sales Help Requisition through your local Univac Representative from Holyoke, Massachusetts. All Holyoke stock will contain this Errata Sheet.

MANAGER, Documentation and Library Services \*Trademark of Sperry Rand Corporation

LISTS: UP-7700.1 to Lists 10U, 217, 630, DATE: April 25, 1969 692 and distribution on Special Bulk Distribution Sheet.

DIVISION OF SPERRY RAND CORPORATION S.P.L.S. P.O. BOX 8100 PHILADELPHIA, PA. 19101

UP-3860 REV. 2

# CONTENTS

| C  | ONTENTS                                                                                                                                                                                                        | i                          |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1. | INTRODUCTION                                                                                                                                                                                                   | 1                          |

| 2. | SYSTEM DESCRIPTION                                                                                                                                                                                             | 2                          |

|    | 2.1. GENERAL                                                                                                                                                                                                   | 2                          |

|    | 2.2. SYSTEM COMPONENTS 2.2.1. Central Processor 2.2.2. Main Storage 2.2.3. Auxiliary Storage 2.2.4. Operator's Control Console                                                                                 | 3<br>3<br>3<br>3<br>4      |

|    | 2.3. CONFIGURATIONS                                                                                                                                                                                            | 5                          |

| 3. | MAIN STORAGE                                                                                                                                                                                                   | 8                          |

|    | 3.1. GENERAL                                                                                                                                                                                                   | 8                          |

|    | 3.2. STORAGE MODULE                                                                                                                                                                                            | 9                          |

|    | 3.3. PACKAGING                                                                                                                                                                                                 | 9                          |

|    | 3.4. STORAGE CAPACITY                                                                                                                                                                                          | 9                          |

|    | 3.5. STORAGE PROTECTION 3.5.1. Storage Protection Modes 3.5.1.1. Privileged Mode 3.5.1.2. User Program Mode                                                                                                    | 10<br>10<br>10<br>10       |

|    | 3.6. RELATIVE ADDRESSING                                                                                                                                                                                       | 11                         |

| 4. | CENTRAL PROCESSOR UNIT                                                                                                                                                                                         | 12                         |

|    | 4.1. GENERAL                                                                                                                                                                                                   | 12                         |

|    | 4.2. PRINCIPAL SECTIONS                                                                                                                                                                                        | 12                         |

|    | 4.3. INSTRUCTION WORD FORMAT 4.3.1. Function Code 4.3.2. Partial-Word or Immediate Operand Designator 4.3.3. Control Register Designator 4.3.4. Index Register Designator 4.3.5. Index Modification Designator | 13<br>13<br>13<br>13<br>13 |

|    | 4.3.6. Indirect Address Designator                                                                                                                                                                             | 13                         |

| 4.4. CONTROL REGISTERS                         | 14 |

|------------------------------------------------|----|

| 4.4.1. Index Registers                         | 14 |

| 4.4.2. Arithmetic Accumulators                 | 15 |

| 4.4.3. Access Control Registers                | 15 |

|                                                | 15 |

| 4.4.4. R Registers                             | 15 |

| 4.4.4.1. RO — Real Time Clock                  | 17 |

| 4.4.4.2. R1 — Repeat Counter                   | 17 |

| 4.4.4.3. R2 — Mask Register                    | 17 |

| 4.5. ARITHMETIC SECTION                        | 17 |

| 4.5.1. The Adder                               | 18 |

| 4.5.2. Arithmetic Accumulators                 | 18 |

| 4.5.3. Partial-Word Transfers                  | 18 |

| 4.5.4. Split-Word Arithmetic                   | 19 |

| 4.5.5. Shifting                                | 19 |

| 4.5.6. Double-Precision Fixed-Point Arithmetic | 20 |

| 4.5.7. Floating-Point Arithmetic               | 20 |

| •                                              | 22 |

| 4.6. EXECUTIVE SYSTEM CONTROL FEATURES         | 22 |

| 4.6.1. Processor State Register                | 24 |

| 4.6.2. Interrupts                              | 24 |

| 4.6.3. Guard Mode                              | 24 |

| 4.7. INSTRUCTION REPERTOIRE                    | 26 |

| 4.7.1. Data Transfer Instructions              | 26 |

| 4.7.2. Fixed-Point Arithmetic                  | 27 |

| 4.7.3. Floating-Point Arithmetic               | 27 |

| 4.7.4. Index Register Instructions             | 28 |

| 4.7.5. Logical Instructions                    | 28 |

| 4.7.6. Shift Instructions                      | 29 |

| 4.7.7. Repeated-Search Instructions            | 29 |

| 4.7.8. Unconditional Jump Instructions         | 30 |

| 4.7.9. Conditional Jump Instructions           | 30 |

| 4.7.10. Test (or Skip) Instructions            | 30 |

| 4.7.11. Executive System Control Instructions  | 31 |

| 4.7.12. Input/Output Instructions              | 31 |

| 4.7.13. Other Instructions                     | 31 |

| 4.7.13. Other instructions                     |    |

| PROCESSOR INPUT/OUTPUT CONTROL SECTION         | 32 |

| 5.1. GENERAL DESCRIPTION                       | 32 |

| 5.2. PERIPHERAL CONTROL                        | 32 |

| 5.3. INTERNALLY SPECIFIED INDEX MODE           | 32 |

| 5.4. EXTERNALLY SPECIFIED INDEX MODE           | 33 |

| 5.5 RUFFER MODE DATA TRANSFERS                 | 35 |

5.

|    | 5.6. INPUT/OUTPUT INFORMATION WORDS 5.6.1. Data Words 5.6.2. Function Words 5.6.3. Identifier Words 5.6.4. Status Words                                                                                                      | 35<br>35<br>36<br>36<br>36 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|    | 5.7. PRIORITY CONTROL                                                                                                                                                                                                        | 36                         |

|    | 5.8. INPUT/OUTPUT INSTRUCTIONS 5.8.1. Monitored Instructions                                                                                                                                                                 | 37<br>37                   |

| 6. | PERIPHERAL SUBSYSTEMS                                                                                                                                                                                                        | 38                         |

|    | 6.1. AVAILABLE PERIPHERAL EQUIPMENT                                                                                                                                                                                          | 38                         |

|    | 6.2. THE FLYING HEAD DRUMS 6.2.1. UNIVAC FH-432/FH-1782 Magnetic Drum Subsystem 6.2.2. UNIVAC FH-432 Magnetic Drum 6.2.3. UNIVAC FH-1782 Magnetic Drum 6.2.4. UNIVAC FH-880 Magnetic Drum                                    | 39<br>40<br>41<br>42<br>43 |

|    | 6.3. FASTRAND MASS STORAGE SUBSYSTEM                                                                                                                                                                                         | 44                         |

|    | 6.4. UNISERVO MAGNETIC TAPE SUBSYSTEMS 6.4.1. UNISERVO VI C Magnetic Tape Subsystem 6.4.2. UNISERVO VIII C Magnetic Tape Subsystem 6.4.3. UNISERVO VIII C/VI C Subsystem 6.4.4. Fully Simultaneous UNISERVO VIII C Subsystem | 47<br>48<br>50<br>51<br>52 |

|    | 6.5. UNIVAC HIGH SPEED PRINTER SUBSYSTEM                                                                                                                                                                                     | 52                         |

|    | 6.6. PUNCHED CARD SUBSYSTEM 6.6.1. UNIVAC Card Reader 6.6.2. UNIVAC Card Punch 6.7. UNIVAC 9300 SUBSYSTEM                                                                                                                    | 54<br>54<br>55             |

|    |                                                                                                                                                                                                                              | 55                         |

| 7. | DATA COMMUNICATIONS                                                                                                                                                                                                          | 57                         |

|    | 7.1. GENERAL                                                                                                                                                                                                                 | 57                         |

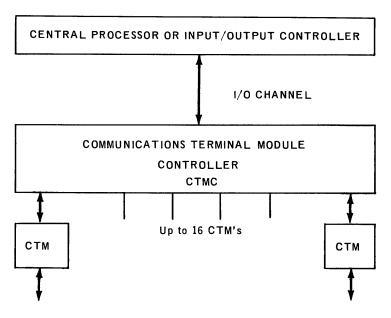

|    | 7.2. UNIVAC 1106 COMMUNICATIONS SUBSYSTEM                                                                                                                                                                                    | 57                         |

|    | 7.3. UNIVAC SYNCHRONOUS DATA TERMINALS 7.3.1. Word Terminal Synchronous 7.3.2. UNIVAC Communication Terminal Synchronous                                                                                                     | 58<br>58<br>59             |

|    | 7.4. UNIVAC DATA COMMUNICATION TERMINAL (DCT) 2000                                                                                                                                                                           | 60                         |

| 7.5. UNISCOPE 300 VISUAL COMMUNICATION TERMINAL SUBSYSTEM 7.5.1. The Keyboard 7.5.2. CRT Display 7.5.3. Subsystem Configurations 7.5.4. Reliability 7.5.5. Special Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63<br>63<br>64<br>64<br>64<br>65                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 7.6. UNIVAC 9200/9300 REMOTE SUBSYSTEMS 7.6.1. The UNIVAC 9200 System 7.6.2. The UNIVAC 9300 System 7.6.3. The UNIVAC Data Communication Subsystem, DCS-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66<br>67<br>67<br>69                                                                                           |

| 8. PROGRAMMED SYSTEMS SUPPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                             |

| 8.1. AVAILABLE SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                                                                                                             |

| 8.2. THE EXECUTIVE SYSTEM 8.2.1. Multiple Modes of Operation 8.2.1.1. Batch Processing 8.2.1.2. Demand Processing (Time-Sharing) 8.2.1.3. Real Time 8.2.1.4. Multiprogramming 8.2.2. Techniques for Utilization of Mass Storage 8.2.3. The Primary Functional Areas of the Executive System 8.2.3.1. Executive Control Language 8.2.3.2. The Supervisor 8.2.3.3. Time Slicing 8.2.3.4. Storage Compacting 8.2.3.5. Facilities Assignment 8.2.3.6. The File-Control System 8.2.3.7. Operator Communications 8.2.3.8. The Diagnostic System 8.2.3.9. Input/Output Device Handlers 8.2.3.10. Auxiliary Processors 8.2.3.11. Utilities 8.2.3.12. System Setup | 70<br>71<br>71<br>71<br>71<br>71<br>72<br>72<br>72<br>72<br>73<br>73<br>73<br>74<br>74<br>74<br>74<br>75<br>75 |

| 8.3. THE ASSEMBLER 8.3.1. Symbolic Coding Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75<br>75                                                                                                       |

| 8.3.2. Assembler Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                                                                                             |

| 8.3.3. Additional Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76                                                                                                             |

| <ul><li>8.4. FORTRAN V</li><li>8.4.1. Language Extensions and Enhancements</li><li>8.4.2. Compiler Organization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76<br>76<br>80                                                                                                 |

| 8.5. CONVERSATIONAL FORTRAN V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81                                                                                                             |

| 8.5.1. System Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81                                                                                                             |

| 8.5.2. System Concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81                                                                                                             |

| 8.5.3. Conversational Processor and the Executive System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82                                                                                                             |

| 8.5.4. Conversational FORTRAN Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82                                                                                                             |

| 8.6. LIFT, FORTRAN II TO FORTRAN V TRANSLATOR                                             | 82                   |

|-------------------------------------------------------------------------------------------|----------------------|

| 8.7. COBOL 8.7.1. The Processor 8.7.2. Special Features                                   | 83<br>84<br>85       |

| 8.8. ALGOL                                                                                | 85                   |

| 8.9. SORT/MERGE                                                                           | 85                   |

| 8.10. MATHEMATICAL FUNCTION PROGRAMS                                                      | 86                   |

| 8.11. APPLICATION PROGRAMS 8.11.1. Linear Programming System 8.11.2. APT III 8.11.3. PERT | 87<br>87<br>88<br>88 |

| 8.12. MATH-PACK                                                                           | 89                   |

| 8.13. STAT-PACK                                                                           | 89                   |

| APPENDICES                                                                                |                      |

| A. NOTATIONAL CONVENTIONS                                                                 | 91                   |

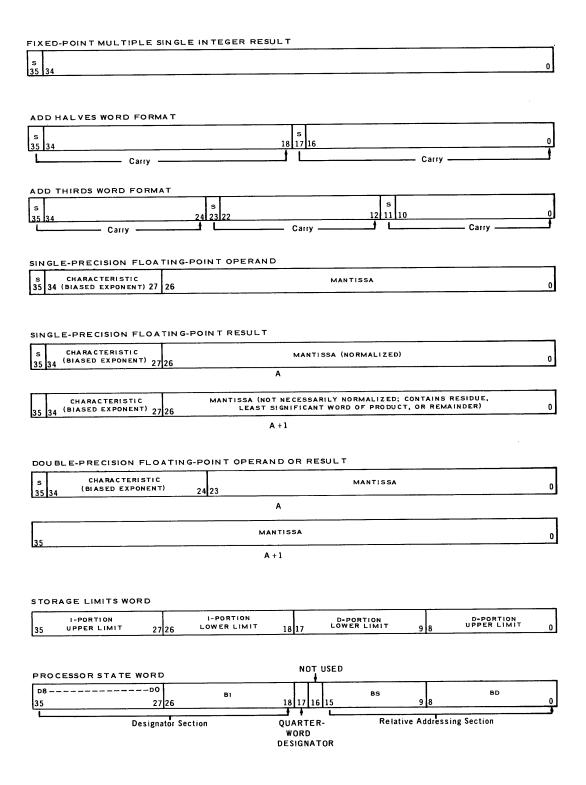

| B. SUMMARY OF WORD FORMATS                                                                | 93                   |

| C. INSTRUCTION REPERTOIRE BY FUNCTION CODE                                                | 95                   |

| D. MATH-PACK ROUTINES                                                                     | 105                  |

| E. STAT-PACK ROUTINES                                                                     | 109                  |

| FIGURES                                                                                   |                      |

| 1-1. The Central Processor and Operator's Console                                         | 1                    |

| 2-1. Minimum Multi-Module Storage Configuration                                           | 6                    |

| 2-2. 262K Multi-Module Storage Configuration                                              | 7                    |

| 4-1. Control Register Address Assignments                                                 | 16                   |

| 4-2. J-Determined Partial Word Operation                                                  | 19                   |

| 4-3. Processor State Register Format                                                      | 23                   |

| 7-1. CTMC Subsystem                                                                       | 57                   |

| TABLES                                                                                    |                      |

| 4-1. Fixed-Address Assignments                                                            | 25                   |

| 7-1. DCT 2000 Field Installable Options                                                   | 61                   |

# 1. INTRODUCTION

A medium-scale extension to the proven UNIVAC 1100 series of computers is provided by the UNIVAC 1106 System. Its modular design provides growth potential within the UNIVAC 1106 as well as possible upgrading to the larger UNIVAC 1108 System.

The UNIVAC 1106 permits the user to select an executive system most applicable to his needs. This selection ranges from EXEC II, which provides a powerful batch processing capability, to the UNIVAC 1106 Executive System with its real-time, multiprogramming, demand, and batch processing ability.

In addition to a versatile executive system, the UNIVAC 1106 utilizes the complete family of UNIVAC 1108 unit processor software, application packages, and peripheral subsystems.

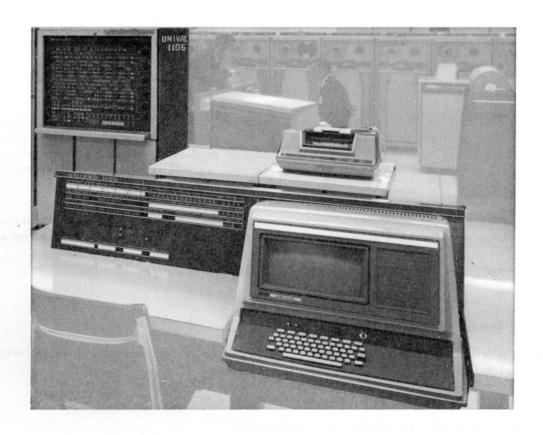

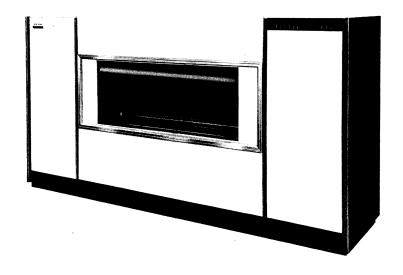

Figure 1-1. The Central Processor and Operator's Console

# 2. SYSTEM DESCRIPTION

#### 2.1. GENERAL

The UNIVAC 1106 System is a general purpose, high performance unit processor system, making good use of the latest advances in computer design, systems organization, and programming technology. Its modular structure permits the selection of systems components to fulfill most efficiently the speed and capacity requirements for applications of varying complexity.

As the workload increases, this modularity also enables the addition of input/output subsystems and main storage. Among the principal features of the 1106 System are:

- Large, modular, parity-checked, high speed main storage

- Program address relocation

- Storage protection

- Partial-word addressability in 6, 9, 12, and 18-bit portions as well as full-word (36 bits) and double-word (72 bits) addressing.

- High speed, random access, auxiliary storage

- Privileged mode for the Executive system

- Guard mode for user programs.

#### 2.2. SYSTEM COMPONENTS

The UNIVAC 1106 System is organized to allow a number of tasks to be performed simultaneously under the direction of a common Executive control system.

The system is composed of four types of components:

- Central Processor

- Main Storage

- Auxiliary Storage Subsystems

- Peripheral Subsystems

# 2.2.1. Central Processor

The processor can perform all functions required for the execution of instructions including arithmetic, input/output, and Executive control. Included in the processor is a set of 166-nanosecond integrated circuit control registers providing multiple accumulators, index registers, input/output access control registers, and specialuse registers.

# 2.2.2. Main Storage

The main storage read/restore cycle time is 1.5 microseconds. The minimum multi-module storage of the UNIVAC 1106 System is 65,536 36-bit words and is expandable up to a maximum of 262,144 words.

# 2.2.3. Auxiliary Storage

The auxiliary magnetic drum storage subsystems are an integral part of each UNIVAC 1106 System. Up to eight FH-432 or FH-1782 magnetic drums, or any combination of the two types, may be attached to one or two control units. Both types of drum can transfer data at 1,440,000 characters per second (240,000 words per second). The average access time of the FH-432 is 4.3 milliseconds; that of the FH-1782 is 17 milliseconds.

# 2.2.4. Operator's Control Console

The UNIVAC 1106 Operator's Control Console subsystem is a free-standing input/output device for directing and monitoring the operation of the CPU. The console is always connected to input/output channel 15.

The basic Control Console includes the following components:

# Display Console

The Display Console contains a keyboard and a Cathode Ray Tube (CRT) display. The keyboard is a standard four-bank keyboard which can generate 63 Fieldata codes. A row of eight interrupt keys is located above the keyboard. The Cathode Ray Tube can display 16 lines of 64 characters each. One UNIVAC PAGEWRITER printer is required for the minimum configuration if this console is selected.

### ■ Day Clock

The day clock on the console displays the time of day in hours, minutes, and hundreths of minutes. It furnishes the time of day to the CPU every 600 milliseconds and sends a day clock interrupt signal to the CPU every 6 seconds. The day clock may be manually disabled from the operator's console.

The day clock may be selected to be active either externally or by program.

# Operator's Control and Indicator Panel

The Operator's Control and Indicator Panel includes fault, disable, and mode indicators for its CPU and associated main storage modules; displays and controls associated with selecting and releasing jumps and stops, with the Program Address Counter and Memory Select Register, and with the time display of the Day Clock. It also includes system controls associated with the CPU and subsystems which are logically connected to the CPU.

# Additional Features

# - Auxiliary Console

An auxiliary right- or left-wing console can be included to accomodate control/display panels for Communication Terminal Module Controller subsystems.

# - UNIVAC PAGEWRITER Printer

The UNIVAC PAGEWRITER printer provides a hard copy of all messages for a permanent record of all completed transactions between the operator and the Executive system. The PAGEWRITER prints lines of up to 80 characters per second.

#### 2.3. CONFIGURATIONS

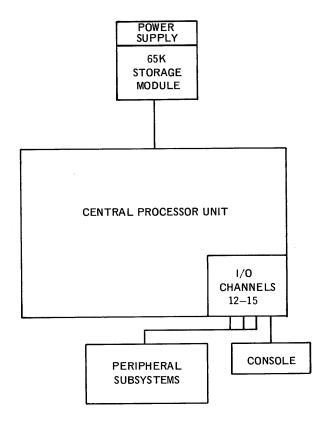

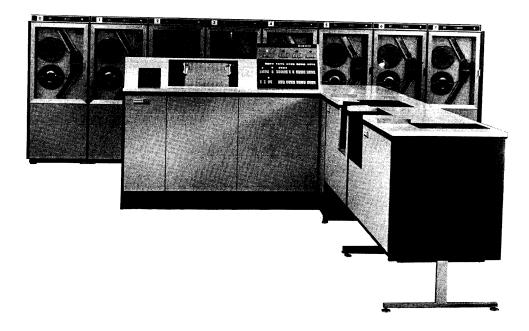

Figure 2-1 depicts the minimum multi-module storage configuration for the UNIVAC 1106 System. The CPU consists of the Command-Arithmetic Section and an Input/Output Section with four I/O channels. Main storage provides 65K 36-bit words. The minimum peripheral subsystems needed to support the software offered are: 1 FH-432/1782 Magnetic Drum Subsystem with 6 FH-432 drums or 1 FH-1782 drum, 1 UNISERVO Magnetic Tape Subsystem with either 4 UNISERVO VI C or 4 UNISERVO VIII C Magnetic Tape Units, an Operator's Console, and 1 online UNIVAC 9300 System.

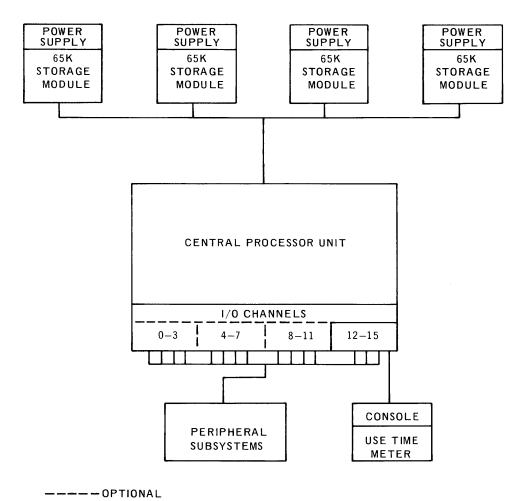

Figure 2-2 illustrates the 262K multi-module storage configuration for the UNIVAC 1106 System.

# CONSOLE AND MINIMUM PERIPHERAL SUBSYSTEMS FOR 1106 OPERATING SYSTEM:

- 1 Operator's Console with:

Display Console and PAGEWRITER Printer

- 1 FH-432/1782 Magnetic Drum Subsystem with: 1 FH-1782 Drum or equivalent

- 1 UNISERVO Magnetic Tape Subsystem with: 4 UNISERVO VI C Magnetic Tape Units; or 4 UNISERVO VIII C Magnetic Tape Units

- 1 Online UNIVAC 9300 System with: 8K Main Storage 132 Print Position Printer Multiplexer I/O Channel 600 cpm 80-Column Card Reader Inter-Computer Control Unit

Figure 2-1. Minimum Multi-Module Storage Configuration

NOTE: EXEC II supports 131K main storage maximum.

Figure 2—2. 262K Multi-Module Storage Configuration

# 3. MAIN STORAGE

#### 3.1. GENERAL

The main storage of the UNIVAC 1106 System is a high performance, fast access repository for instructions and data. Its design fully supports the concepts of multiprogramming, modularity, and reliability around which the entire UNIVAC 1106 System is constructed. Among its featured characteristics are:

- 1.5 microsecond read/restore cycle time

- 65,536, 98,304, 131,072, 196,608, or 262,144 36-bit words of multi-module storage

- Parity checking on all storage references

- Hardware storage protection lockout boundaries establishable in 512-word increments

- Relative addressing and dynamic program relocatability through program base registers

- Online serviceability multi-module storage pairs may be removed for servicing withou stopping the entire system.

Main storage performs the following functions:

- Accepts an address from the processor.

- Stores or retrieves a word at that address

- Issues an acknowledgement signifying that a storage reference has been completed

- Checks parity on all data and delivers an interrupt signal to the processor should a parity error occur.

The modular storage concept has significant advantages for the immediate as well as the future needs of the system. Addition of banks of storage is simplified. It becomes a simple matter to add storage elements, or to replace them with improved equipment bank by bank, as technology advances.

#### 3.2. STORAGE MODULE

Each module of multi-module storage includes 32,768 words of ferrite core array. Each word is 36 bits long, and carries two additional parity bits in nonaddressable levels, one bit for each half word. The main components of the module are a 15-bit address register, a 36-bit read/restore register, parity checking circuits, and request/acknowledge circuits.

The 15-bit address register of each storage module provides addressing for 32,768 words. Since an 18-bit address is generated within the processor at each storage reference, three bits are available for selection of one of the four possible storage modules.

Parity is checked on reading or calculated on writing for each storage access. If a parity error is detected, the storage bank sends a parity error interrupt signal to the processor and rewrites the word in its incorrect form to ensure subsequent data errors when the word is again referenced. Preservation of the error in this way facilitates fault location, since the Executive can determine whether the failure is transient or is associated with a marginal or complete failure of the module.

#### 3.3. PACKAGING

For multi-module storage, one or two 32,768-word storage modules (module pair) within a single cabinet constitute a bank. An adjacent cabinet contains DC power supplies for operation of the bank.

# 3.4. STORAGE CAPACITY

Available multi-module storage capacity ranges from 65,536 words to the system maximum of 262,144 words in accordance with the following:

65,536 words (two modules) — Minimum for system 98,304 words (three modules) 131,072 words (four modules) 196,608 words (six modules) 262,144 words (eight modules) — Maximum for system

#### 3.5. STORAGE PROTECTION

To prevent inadvertent program reference to out-of-range storage addresses, the 1106 processor includes a hardware storage protection feature. The controlling element in this feature is the Storage Limits Register, the contents of which are as follows:

|    | INSTRUCTION AREA  |                   |    |    |                   | DAT | A AREA            |   |

|----|-------------------|-------------------|----|----|-------------------|-----|-------------------|---|

|    | UPPER<br>BOUNDARY | LOWER<br>BOUNDARY |    |    | UPPER<br>BOUNDARY |     | LOWER<br>BOUNDARY |   |

| 35 | 27                | 26                | 18 | 17 | ·                 | 9   | 8                 | 0 |

The Storage Limits Register (SLR) can be loaded by the Executive system to establish allowable operating areas for the program currently in execution. These areas are termed the program instruction (I) and data (D) areas. Before control is given to a particular program, the Executive loads the SLR with the appropriate I and D boundaries.

Before each main storage reference, the processor performs a limits check on the address, comparing against the limits of either the I or D field of the SLR. An out-of-limits address generates a guard mode interrupt, thereby allowing the Executive to regain control and take appropriate action.

# 3.5.1. Storage Protection Modes

The Executive system can establish two different modes of storage protection by means of control fields in the Processor State Register (PSR) described in Section 4. Normally, the Executive itself operates in open mode; that is, the Storage Limits Register may be loaded but the PSR is set to disregard this, and the Executive can reference any location in main storage.

#### 3.5.1.1. Privileged Mode

Another mode can be established in the PSR for privileged programs. This privileged mode protects against out-of-bounds writes. Privileged programs (such as real-time programs or Executive-controlled subroutines) may enter non-alterable (re-entrant) subroutines, which are part of the Executive. Though these privileged programs are assumed to be thoroughly checked out, the system is still fully protected against unexpected occurrences since write protection is in effect.

#### 3.5.1.2. User Program Mode

In the user program mode, read, write, and jump storage protection is in effect. Therefore, user programs are limited to those areas assigned by the Executive. If the user program reads, writes, or jumps to an out-of-limits address, an interrupt returns control to the Executive for remedial action.

Read/jump protection allows the Executive to stop the program at the point of error, terminate it, and provide diagnostic information to the programmer thereby minimizing wasted time and smoothing the checkout process.

# 3.6. RELATIVE ADDRESSING

Relative addressing is a feature of great significance in multiprogramming, time-sharing, and real-time operations, for it allows storage assignments for one program (the one going into execution) to be changed dynamically by the Executive to provide continuous storage for operation of another program, and it permits programs to dynamically request additional main storage according to processing needs. An additional advantage is that systems programs stored in auxiliary storage may be brought in for operation in any available area without complicated relocation algorithms.

Relative addressing is provided for through base registers contained within the CPU. Two separate registers control the basing of the program instruction and data bank, and a third register controls the selection of the appropriate base register.

# 4. CENTRAL PROCESSOR UNIT

#### 4.1. GENERAL

The UNIVAC 1106 Central Processor Unit (CPU) is the principal component of the UNIVAC 1106 System and, generally, the one by which the entire system is identified. It can operate under Executive or user program modes of control; it performs both arithmetic and logical operations; and it accommodates and supervises up to 16 input/output channels.

#### 4.2. PRINCIPAL SECTIONS

The processor is logically divided into six interacting sections each of which is identified and briefly described below.

- Control Registers The CPU has 128 program-addressable control registers used for arithmetic operations, indexing, and input/output buffer control.

- Arithmetic Section This section contains the adder registers, and control circuits necessary for performing fixed and floating point arithmetic, partial-word selection, shifting, logical operations, and tests.

- Control Section This section provides the basic control and logic for instruction decoding and execution. It includes the Program Address Counter used for the sequential accession of instructions; the Program Control Register in which instructions are staticized for execution; and the Processor State Register (PSR), which determines various processor operating modes. The Control Section also services interrupts.

- Input/Output Section This section controls and multiplexes data flow between main storage and 16 input/output channels. It includes an interrupt priority network and paths to peripheral subsystems for both function signals and data.

- Indexing Section This section contains parallel index adders and threshold test circuitry. It is used generally for processor control functions, operand address development, program relocation, and input/output transfer control.

- Storage Class Control Section The Storage Class Control section receives the final operand address from the index adder and establishes address and data paths to one of eight possible storage modules. Storage Class Control also determines whether a final address refers to a control register.

#### 4.3. INSTRUCTION WORD FORMAT

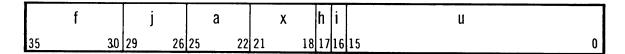

The format of the 1106 instruction word is illustrated below followed by an explanation of each field. Some fields have more than one meaning depending on the class of instruction.

# 4.3.1. Function Code

These six bits specify the operation to be performed. For function codes above 70<sub>8</sub>, the f and j fields are combined to produce a 10-bit function code. An illegal function code generates an interrupt.

## 4.3.2. Partial-Word or Immediate-Operand Designator

For function codes less than 70<sub>8</sub>, the j designator specifies partial-word or immediate-operand selection. (See Figure 4-2 for specific partial-word selections.)

# 4.3.3. Control Register Designator

The four-bit a field designates which control register, within a group selected by the function code, is involved in the operation. For some operations, the a field refers to an arithmetic register; for others, it refers to either an index register or some other control register. In input/output instructions, it specifies the channel and its associated input or output access control register. For function code 708 the a and j designators together address one of the 128 control registers.

# 4.3.4. Index Register Designator

The x field specifies one of the 15 index registers to be used in address modification. When register 00 is designated, indexing is suppressed.

#### 4.3.5. Index Modification Designator

The h field controls modification of the index value (Xm) by the increment field (Xi) after indexing (see 4.4.1). If h = 1, the right half of the index register is modified by the contents of its left half; if h = 0, modification is suppressed.

#### 4.3.6. Indirect Address Designator

The i designator controls the use of indirect addressing during instruction execution. If i=0, the instruction functions normally. If i=1, the 22 least significant bit positions of the instruction (x, h, i and u fields) are replaced in the instruction register with the contents of the 22 least significant bit positions of the word at the effective address. Indirect addressing continues as long as i=1 with full indexing capability at each level.

#### 4.3.7. Address Field

The u field normally specifies the operand address. However for certain instructions it holds constants. For example, the shift instructions use the seven least significant bit positions to hold the shift count. In all instructions, the value in the u field may be modified by the contents of an index register.

#### 4.4. CONTROL REGISTERS

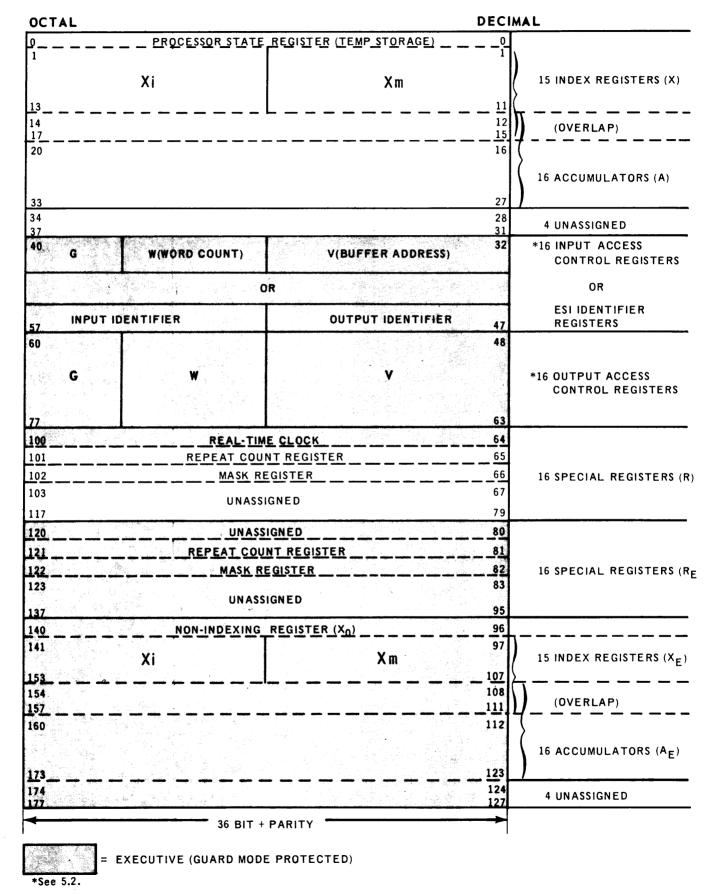

The 128 program-addressable control registers are grouped to provide multiple index registers, accumulators, input/output access control registers, and special registers (see Figure 4-1).

The control registers consist of 36-bit integrated-circuit registers, with a basic cycle time of 166 nanoseconds. Two parity bits are included with each control register.

Effective use of multiple accumulators and index registers for the development and use of constants, index values, and operands substantially improves performance. UNIVAC 1106 compilers, for example, perform significantly better through multiple register usage, and can produce highly efficient code.

In the following descriptions only programmable registers are discussed. The Executive, through modes established by the Processor State Register, has exclusive use of the duplicate set of control registers as well as the Access Control Registers indicated by the shaded areas in Figure 4-1.

# 4.4.1. Index Registers

Control register locations 00-15 are Index Registers and have the following format:

|    | Xi                              |    |    | X <sub>m</sub> |   |

|----|---------------------------------|----|----|----------------|---|

| 35 | MODIFIER INCREMENT OR DECREMENT | 18 | 17 | INDEX MODIFIER | 0 |

The Xm portion of the index register is an 18-bit modifier to be added to the base operand address of the instruction. The Xi portion of the index word updates the Xm portion, after base operand address modification.

Index register modification is specified by a 1 bit in the h field of the instruction, while indexing itself is specified by a nonzero value in the x field. Both functions take place within the basic instruction execution cycle.

When cascaded indirect addressing is used in a programmed operation, full indexing capabilities are provided at each level. Indirect addressing replaces the x, h, i and u portions of the instruction register, beginning with a new indexing cycle for each cascaded sequence. This process continues until the i field is zero.

#### 4.4.2. Arithmetic Accumulators

Control register locations 12-27 are arithmetic accumulators, for programmed storage of arithmetic operands and results. The computation is performed in nonaddressable transient registers within the arithmetic section.

Depending upon the instruction, use of the accumulators results in a variety of word formats. Double precision instructions and a number of logical instructions reference two contiguous accumulators, i.e., A and A + 1. In arithmetic operations, A + 1 always holds the least significant part of an operand or result. Some instructions, such as single precision floating point operations, call on a oneword operand from memory but produce a two-word result in the specified A and A + 1.

# 4.4.3. Access Control Registers

Control register locations 32-63 are Input and Output Access Control Registers (ACR's). They are guard mode protected and may be referenced only by the Executive. Formats of the Access Control Words are detailed in Section 5.

The word-by-word transmission of data over an I/O channel is governed by the contents of the ACR's. Two ACR's, one for input and one for output, are assigned to each of the sixteen channels. Input ACR's (locations 32-47) control input data transfers while output ACR's (locations 48-63) govern the transmission of output data and Function Words.

When an input/output operation is initiated, the programmed ACR word is loaded into the ACR corresponding to the channel associated with the specified peripheral unit.

#### 4.4.4. R Registers

The sixteen control register locations 64-79 are R Registers. The first three of these (R0, R1, R2) have specified functions and formats as described below. The remaining R Registers are not specifically assigned; typically they are used as loop counters, transient registers, or storage for intermediate values or constants.

#### 4.4.4.1. R0 - Real Time Clock

| 35 | UNASSIGNED | 18 17 | CLOCK COUNT | 0 |

|----|------------|-------|-------------|---|

| 33 |            | 10 17 |             |   |

This register is initially loaded by the program. The contents are then decremented once each 200 microseconds. A real time clock interrupt occurs when the clock count goes through zero. Thus, if the clock is initially loaded with the value 5000, an interrupt occurs in exactly one second.

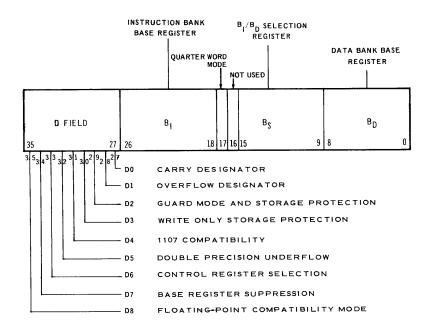

Figure 4-1. Control Register Address Assignments

#### 4.4.4.2. R1 - Repeat Counter

| UNASSIGNED | REPEAT COUNT(k) |

|------------|-----------------|

| 35         | 17 0            |

The Repeat Counter controls repeated operations such as Block Transfer and Search instructions. To execute a repeated instruction k times, the repeat counter is loaded with k prior to the execution of the instruction.

#### 4.4.4.3. R2 - Mask Register

The Mask Register functions as a filter in determining which portions of words are to be tested in repeated masked search operations or in logical comparisons. The contents of the effective address are compared to the contents of the Arithmetic Register only with respect to those positions which contain one's in the Mask Register. In repeated masked search operations, both the Mask Register and the Repeat Counter are loaded prior to executing the search command.

#### 4.5. ARITHMETIC SECTION

In the UNIVAC 1106 System the manipulation of data (addition, subtraction, multiplication, division, shifting) takes place in the arithmetic section of the central processor. During the execution of an arithmetic instruction, storage registers within the arithmetic section itself are used for actual computation. The arithmetic section has the following characteristics:

- On fixed point, single precision instructions, the j designator selects all or a portion of one of the operands (half, third, quarter or sixth word) for use in the arithmetic operation.

- Special split-word arithmetic instructions provide for simultaneous addition or subtraction of corresponding half or third words of the two operands.

- When a shift matrix is used, a multiposition shift requires the same time as a one place shift. Right and left shifts of single or double length operands can be specified. Left shifting is logical (zeros are filled to the right). Right shifts may be either logical or algebraic (sign bits are filled to the left).

- Sixteen arithmetic registers in the control register section, acting as sixteen accumulators, allow parallel and cumulative computation. Full double precision floating point arithmetic is provided by the double precision expansion kit.

- When the results of arithmetic operations are in double-length form, they are automatically stored in consecutive control registers and are available for retrieval as double-length results.

- Alphanumeric comparisons utilizing the Mask Register allow any selection of bits in one 36-bit word, to be directly compared with corresponding bits of another word.

#### 4.5.1. The Adder

The adder in the 1106 Processor is a one's complement subtractive adder for 36-bit or 72-bit operations. For purposes of analysis and debugging, the programmer may manually simulate the computer operation by simple binary or octal addition.

Two special internal designators associated with the arithmetic adder are the overflow designator and the carry designator. The fixed point addition and subtraction instructions, single and double precision, are the only instructions which affect these two designators.

Before the execution of any of these instructions, both designators are cleared. The overflow designator is set when a significant bit is generated in the sign position. Thus, a positive result from two negative quantities or a negative result from two positive quantities sets the overflow designator. The carry designator is set whenever an end-around carry is generated. This indicates the involvement of a negative quantity as one of the operands.

After the instruction has been performed, the settings of the designators remain unchanged until another of the designated arithmetic instructions is initiated. Both designators are set in time to be tested immediately after the specified instruction has been executed.

When an interrupt occurs, the hardware stores the settings of the carry and overflow designators in the Processor State Register (see 4.6.1) and control passes to the Executive system. This information is automatically returned to the designators when the Executive returns control to the interrupted program.

#### 4.5.2. Arithmetic Accumulators

The sixteen arithmetic accumulators can be addressed directly by the programmer and are available for storing operands and results of arithmetic computations. These arithmetic accumulators should not be confused with the non-addressable transient registers that are used in actual computation and are contained within the arithmetic section itself.

With the Add to X and Add Negative to X instructions, the index registers also act as accumulators in the same manner as the arithmetic registers.

#### 4.5.3. Partial-Word Transfers

To minimize shifting and masking and to allow computation based on selected portions of words, the 1106 System permits the transfer of partial words into and out of the arithmetic section in a varying pattern (see Figure 4-2).

By selecting the coding of the j designator in the instruction word and bit 17 of the Processor State Register a programmer may transfer a chosen portion of an operand to or from a control register or the arithmetic section. The transfer to an arithmetic register may also be accompanied by sign extension for subsequent arithmetic operations, depending on the j designator.

| J<br>(OCTAL) | PSR<br>BIT 17 | BIT POSITIONS OF<br>(U)→ A, X, or R | BIT POSITIONS OF (A), (X), or (R) $\longrightarrow$ U |

|--------------|---------------|-------------------------------------|-------------------------------------------------------|

| 00           | -             | 35-00 → 35-00                       | 35-00 35-00                                           |

| 01           | _             | 17-00 17-00                         | 17-00 17-00                                           |

| 02           | - 1           | 35–18 → 17–00                       | 17-00 35-18                                           |

| 03           | -             | 17-00 → \$ 17-00                    | 17-00 17-00                                           |

| 04           | 0<br>1        | 35-18 → \$ 17-00<br>26-18 → 08-00   | 17-00 35-18<br>08-00 16-18                            |

| 05           | 0<br>1        | 11-00 → S 11-00<br>08-00 → 08-00    | 11-00 11-00<br>08-00 08-00                            |

| 06           | 0<br>1        | 23-12 → \$ 11-00<br>17-09 → 08-00   | 11-00 23-12<br>08-00 17-09                            |

| 07           | 0<br>1        | 35-24 → S 11-00<br>35-27 → 08-00    | 11-00 35-24<br>08-00 35-27                            |

| 10           | -             | 05-00 05-00                         | 05-00 05-00                                           |

| 11           | -             | 11-06 05-00                         | 05-00 11-06                                           |

| 12           | -             | 17-12 05-00                         | 05-00 17-12                                           |

| 13           | -             | 23-18 05-00                         | 05-00 23-18                                           |

| 14           | -             | 29-24 05-00                         | 05-00 29-24                                           |

| 15           | -             | 35–30 → 05–00                       | 05-00 35-30                                           |

| 16           | -             | 18 bits* <del>→</del> 17-00         | NO TRANSFER                                           |

| 17           | _             | 18 bits* → \$ 17-00                 | NO TRANSFER                                           |

<sup>\*</sup> If x = 0, h, i, and u are transferred If  $x \neq 0$ ,  $u + (X_x)_m$  is transferred

S = Sign Extension, where the sign is that of the j-determined final contents of A.

Figure 4-2. J-Determined Partial Word Operation.

#### 4.5.4. Split-Word Arithmetic

The System can perform addition and subtraction of half words or third words simultaneously. The right halves of two operands, for example, are added and the sum is stored in the right half of the selected accumulator. At the same time, the left halves of the same two operands are added and the result is stored in the left half of the same accumulator. There is no carry interaction between the halves. The same holds true for thirds of words. Each partial word operates as an independent arithmetic register, with its own end-around carry.

# 4.5.5. Shifting

The System can perform both single-length shifting (36 bits) or double-length shifting (72 bits), treating the latter as if operating with a single 72-bit register. A high speed shift matrix makes execution time independent of the number of places involved in the shift, which means that an operand can be shifted from 0 to 72 positions in one storage cycle time.

Six types of shift operations are provided.

- Right Circular bits shifted out at the right reappear at the left.

- Left Circular bits shifted out at the left reappear at the right.

- Right Logical zeros replace bits shifted out of the most significant positions.

- Left Logical zeros replace bits shifted out of the least significant positions.

- Right Algebraic sign bits replace bits shifted out of the most significant positions.

- Scale-Factor Shift a single or double accumulator left shift which positions the word and simultaneously counts the number of shifts required until the most significant bit of the accumulator is unequal to the next most significant bit.

#### 4.5.6. Double Precision Fixed Point Arithmetic

The System provides 72-bit, double precision fixed point addition and subtraction. Operands are processed as if they occupied a single 72-bit register. Bit 71, the high order bit, is the sign bit.

In addition, several arithmetic instructions produce two-word results. With fixed point multiplication, a double-length product is stored in two arithmetic registers for integer and fractional operations. Integer and fractional division is performed upon a double-length dividend with the quotient retained in A and the remainder retained in A+1.

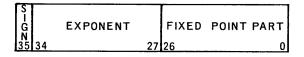

# 4.5.7. Floating Point Arithmetic

The System is equipped with an extensive hardware repertoire of floating point instructions. If the arithmetic is single precision, the range is from  $10^{38}$  to  $10^{-37}$  with eight-digit precision. The word formats are given below.

Source Operand Format

Result Format

G EXPONENT FIXED POINT PART N 35 34 27 26 0

WORD 1

WORD 2

In a single-precision floating point operation word 1 is the more significant portion of the result. Word 2 contains the less significant portion. Mathematical error tracing can determine how much accuracy is being lost in calculations using this format. The least significant word is displaced 27 bits to the right of the binary point in the significant word. Hence, its exponent is always adjusted by -27. The two-word result of this single precision operation is developed in two contiguous Arithmetic Registers.

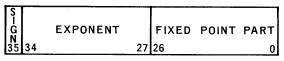

If the arithmetic is double precision, the range is from  $10^{307}$  to  $10^{-308}$  with 18 digit precision. The values are expressed in two adjacent words, as shown in the following format.

Source and Result Format

| SIG        | EXPONENT |       | FIXED | POINT PART |   |

|------------|----------|-------|-------|------------|---|

| N<br>35 34 |          | 25 24 | 0     | 35         | 0 |

Full double precision operations do not require a repeated sign and exponent in the 36 least significant bits.

In any of the floating point formats the exponent can assume a range of values as follows:

Single precision (8 bits): 000-255

Double precision (11 bits): 0000-2047

To express negative exponents, the hardware biases (floats) the exponent on a midvalue. The sign bit of the floating-point word applies to the fixed-point part. The true and biased ranges of the exponent are as follows:

|                  | True                         | Biased          |

|------------------|------------------------------|-----------------|

| Single precision | $-128_{10}$ to $+127_{10}$   | $0 - 255_{10}$  |

| Double precision | $-1024_{10}$ to $+1023_{10}$ | $0 - 2047_{10}$ |

A positive fixed point part is normally assumed to be in range  $\frac{1}{2}$  to 1. Such a value places a 1 bit in the most significant bit position. When this condition exists, the floating point number is said to be normalized. A negative fixed point part causes the entire floating point word to be complemented, and a 0 appears in this position.

Floating point instructions are also provided for the following operations.

Determining differences in exponents.

Packing and unpacking exponents and fixed point parts (single and double precision).

Conversion - Single to double precision

Double to single precision

# 4.6. EXECUTIVE SYSTEM CONTROL FEATURES

The Executive has complete control of the entire 1106 system. Special hardware features are provided to permit this control.

The integrity of the system is maintained by Guard Mode operation. In this mode, certain instructions, registers, and storage locations are available for the exclusive use of the Executive System.

#### 4.6.1. Processor State Register

The Processor State Register (PSR) stores a 36-bit representation of various states and conditions affecting the current operations of the Processor. By means of this register the Executive sets up control modes for itself, governs the operation of worker programs, and registers status information concerning worker programs when it regains control in consequence of interrupts. Figure 4–3 explains in detail the significance of each bit of the PSR.

The Executive uses a special instruction, Load Processor State Register, to load the PSR and to govern the following functions and conditions:

- Program base addresses

- Quarter word operations in the processor

- Carry and overflow status

- Guard Mode

- Storage protection mode

- 1107 compatibility mode

- Floating point underflow mode (double precision operations)

- Base register suppression

- Control register process selection

- IBM 7090 floating point compatibility mode

The contents of the PSR are stored automatically as soon as an interrupt occurs. Program carry and overflow status are first registered in the PSR and then its contents are transferred to Control Register location 00 (Index Register zero). The PSR is then cleared in preparation for Executive operations. The Executive saves the contents of Control Register 00 so that it can reinstate conditions as control is returned to the program that was interrupted.

#### D FIELD

# D8 7090 FLOATING-POINT COMPATIBILITY MODE

- =0 Clears exponent to zero when a fixed point part equal to zero is generated

- =1 Produces relative floating point 0

#### D7 BASE REGISTER SUPPRESSION

- =0 Allows contents of Base Registers to be added to every U address.

- =1 Base Register addition on storage reference is suppressed when instruction i-designator = 1.

# D6 CONTROL REGISTER SECTION

- =0 Selects User Program control Register Set

- (Locations 00-37<sub>8</sub>, 100-117<sub>8</sub>) =1 Selects Executive Control Register Set (Locations 120-177<sub>8</sub>)

The Executive passes control to User Programs with bit 33 = 0, which selects the worker set. An interrupt forces this bit to 1 after (PSR) has been transferred to X0, making the upper Control Registers available to the Executive.

# D5 DOUBLE PRECISION UNDERFLOW - Double Precision Floating Point Operations

- =0 Interrupts on D.P. Floating Underflow

- =1 Clears results to zero and continues

This is a program-requestable option which is set up for the program by the Executive.

#### D4 1107 COMPATIBILITY MODE

- =0 1106 Mode Full Range Addressing

- =1 The upper two bits of the effective address (U) are stripped, allowing 1107 program compatibility with the 1106. In this mode, only 65,536 words of storage are available.

#### D3 WRITE-ONLY STORAGE PROTECTION

- = 0 Read, Write and Jump storage protection under Guard Mode

- =1 Write Protection Only under Guard Mode

#### D2 GUARD MODE

- =0 Guard Mode off. All instructions and storage references to Access Control Registers (40-77<sub>8</sub>), the Real Time Clock (100<sub>8</sub>) and Executive Control Registers (120-177<sub>8</sub>) are permitted.

- =1 Guard Mode on. Invalidates all instructions and control register references described above to enforce the integrity of the system. Only when Guard Mode is on are the contents of the storage limits register effective in storage protection. (If D3 = 1, there is no read or jump protection.)

#### D1 OVERFLOW DESIGNATOR

=1 Arithmetic Overflow at time of interrupt.

#### DO CARRY DESIGNATOR

=1 Arithmetic Carry at time of interrupt

#### OTHER FIELDS

0-8

9-15

BASE REGISTERS. These registers

provide the absolute base address values

on which programs "float" in storage

during execution.

#### 17 QUARTER-WORD MODE BIT

- =1 Quarter-word mode effective

- =0 Quarter-word mode not effective.

Figure 4-3. Processor State Register Format

# 4.6.2. Interrupts

The interrupt network of the UNIVAC 1106 System is extensive. The interrupt is a control signal generated by either a peripheral subsystem (external interrupt) or the control section of the central processor. Specific interrupt locations are assigned within the lower regions of main storage for each condition. These interrupt locations are programmed to capture the interrupted address and enter interrupt response subroutines in the Executive System. The symchronization of input/output activities and response to real time situations is accomplished through some of these interrupts.

Other interrupts are provided for certain error conditions within the central processor. These may result from a programming fault such as an illegal instruction, a main storage parity error, or a user program violation such as an attempt to write into a protected area of storage or a violation of guard mode. These fault interrupts signal the Executive to initiate remedial or terminating action when they are encountered. Table 4-1 lists the fixed-address assignments. Note that they are all interrupt locations except for 2008, which receives the status word, and 2168, which stores the day clock count.

#### 4.6.3. Guard Mode

The Guard Mode prevents user programs from executing any of the instructions listed below. These are reserved for the Executive. It also protects certain locations in main storage reserved for Executive operations.

Guard Mode is established by the Load Processor State Register instruction. Execution of this instruction with the appropriate PSR bit pattern is the only way that Guard Mode can be made operative and provides the only direct access to the PSR. Under Guard Mode, an attempt to perform any of the privileged instructions or functions listed below results in a processor interrupt.

- Load Processor State Register

- Load Storage Limits Register

- Select Interrupt Location

- Load Channel Select Register

- Halt Instructions

- All I/O Instructions

- Disabling of I/O interrupts for more than 100 microseconds

- Attempting to write into any of the Executive control registers (32-64 or 80-127)

Guard Mode is disabled by the occurrence of any interrupt.

| DECIMAL<br>ADDRESS | OCTAL<br>ADDRESS | FIXED ASSIGNMENT                                     |

|--------------------|------------------|------------------------------------------------------|

| 128                | 200              | Status Word for External Interrupt on CPU #0         |

| 129                | 201              | Unassigned                                           |

| 130                | 202              | Unassigned                                           |

| 131-135            | 203-207          | Unassigned                                           |

| 136                | 210              | Power Loss Interrupt                                 |

| 137                | 211              | ESI Access Control Word Parity Error Interrupt       |

| 138                | 212              | ISI Access Control Word Parity Error Interrupt       |

| 139                | 213              | I/O Data Parity Error Interrupt                      |

| 140-141            | 214-5            | Unassigned                                           |

| 142                | 216              | Day Clock Input                                      |

| 143                | 217              | Day Clock Interrupt                                  |

| 144                | 220              | ISI Input Monitor Interrupt                          |

| 145                | 221              | ISI Output Monitor Interrupt                         |

| 146                | 222              | ISI Function Monitor Interrupt                       |

| 147                | 223              | ISI External Interrupt                               |

| 148                | 224              | ESI Input Monitor Interrupt                          |

| 149                | 225              | ESI Output Monitor Interrupt                         |

| 150                | 226              | Unassigned                                           |

| 151                | 227              | ESI External Interrupt                               |

| 152                | 230              | Unassigned                                           |

| 153                | 231              | Real Time Clock Interrupt                            |

| 154                | 232              | Unassigned                                           |

| 155                | 233              | Unassigned                                           |

| 156                | 234              | Unassigned                                           |

| 157                | 235              | Main Storage Parity Error Interrupt (Bank #1)        |

| 158                | 236              | Main Storage Parity Error Interrupt (Bank #2)        |

| 159                | 237              | Main Storage Parity Error Interrupt (Bank #3)        |

| 160                | 240              | Control Register Parity Error Interrupt              |

| 161                | 241              | Illegal Instruction Interrupt                        |

| 162                | 242              | Executive Return Interrupt                           |

| 163                | 243              | Guard Mode/Storage Limits Progection Fault Interrupt |

| 164                | 244              | Test and Set Interrupt                               |

| 165                | 245              | Floating-Point Characteristic Underflow Interrupt    |

| 166                | 246              | Floating-Point Characteristic Overflow Interrupt     |

| 167                | 247              | Divide Fault Interrupt                               |

| 168-255            | 250-377          | Unassigned                                           |

| Last address       | -1               | Main Storage Parity Error Interrupt (Bank #0)        |

Table 4-1. Fixed-Address Assignments

# 4.7. INSTRUCTION REPERTOIRE

The UNIVAC 1106 Processor is provided with an unusually powerful and flexible instruction repertoire. Many of the instructions are effectively access and completed in the time of one storage cycle. Included in the complete set of instructions is a group which permits fast and simplified control by the Executive System.

In the following discussion, the instructions in the UNIVAC 1106 repertoire are grouped by functional class to illustrate the power of the repertoire. Appendix C lists them numerically by octal function code, stating exactly what each one does. The octal codes are listed here to facilitate reference to Appendix C.

# 4.7.1. Data Transfer Instructions

To load the Arithmetic registers:

| Load A                    | 10 |

|---------------------------|----|

| Load Negative A           | 11 |

| Load Magnitude A          | 12 |

| Load Negative Magnitude A | 13 |

To load the Index and R registers:

| Load R           | 23 |

|------------------|----|

| Load X           | 27 |

| Load X Modifier  | 26 |

| Load X Increment | 46 |

To load two Arithmetic registers with one instruction:

| Double Load A           | 71,13 |

|-------------------------|-------|

| Double Load Negative A  | 71,14 |

| Double Load Magnitude A | 71.15 |

To store the Arithmetic registers:

| Store A           | 01 |

|-------------------|----|

| Store Negative A  | 02 |

| Store Magnitude A | 03 |

To store other control registers

| Store X | 06 |

|---------|----|

| Store R | 04 |

To store two Arithmetic registers with one instruction:

| Double Store A                 | 71, 12 |

|--------------------------------|--------|

| Two special purpose transfers: |        |

| Store Zero     | 05 |

|----------------|----|

| Block Transfer | 22 |

All transfer instructions, except double-length transfers, move selected parts of words. That is, the partial-word feature allows any sixth, quarter, third, or half word to be loaded into the lower portion of an arithmetic register when using Load instructions. Similarly, when using a Store instruction, any sixth, quarter, third or half word can be transmitted from the lower portion of an arithmetic register, index register, or R Register to main storage.

#### 4.7.2. Fixed Point Arithmetic

Single-word operations on arithmetic registers:

| Add to A                    | 14   |

|-----------------------------|------|

| Add Negative to A           | 15   |

| Add Magnitude to A          | 16   |

| Add Negative Magnitude to A | 17   |

| Add Upper                   | 20   |

| Add Negative Upper          | 21   |

| Multiply Integer            | 30   |

| Multiply Single Integer     | . 31 |

| Multiply Fractional         | 32   |

| Divide Integer              | 34   |

| Divide Single Fractional    | 35   |

| Divide Fractional           | 36   |

# Double length operations on two arithmetic registers:

| Double Precision | Fixed Point Add          | 71,10 |

|------------------|--------------------------|-------|

| Double Precision | Fixed Point Add Negative | 71,11 |

#### Special format operations:

| Add Halves          | 72,04 |

|---------------------|-------|

| Add Negative Halves | 72,05 |

| Add Thirds          | 72,06 |

| Add Negative Thirds | 72,07 |

| Add to X            | 24    |

| Add Negative to X   | 25    |

#### 4.7.3. Floating Point Arithmetic

The repertoire includes both single and double precision floating point operations, using one-word and two-word operands, respectively. Ones complement arithmetic is used.

# Single Precision

| Floating Add                 | 76,00 |

|------------------------------|-------|

| Floating Add Negative        | 76,01 |

| Floating Multiply            | 76,02 |

| Floating Divide              | 76,03 |

| Load and Unpack Floating     | 76,04 |

| Load and Convert to Floating | 76,05 |

# Double Precision

| Double Precision Floating Add          | 76.10 |

|----------------------------------------|-------|

| Double Precision Floating Add Negative | 76,11 |

| Double Precision Floating Multiply     | 76,12 |

| Double Precision Floating Divide       | 76,14 |

| Double Load and Convert to Floating    | 76.15 |

#### Miscellaneous

| Magnitude of Characteristic Difference to Upper | 76,06 |

|-------------------------------------------------|-------|